The Innosilicon MIPI C-PHY/D-PHY combo IP is designed to combine both C-PHY and D-PHY function into one integrated IP. The combo PHY shares as much as possible logic/pads, and extends its compatibility to most flexible applications.

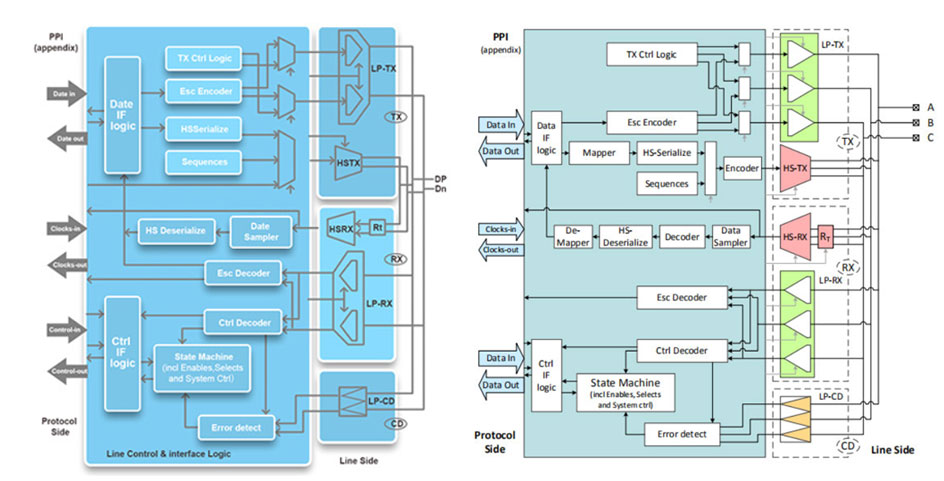

The Innosilicon MIPI C-PHY/D-PHY combo is compatible with MIPI D-PHY 2.0 specification is a high-frequency low-power, low-cost, source-synchronous, physical Layer. The PHY can be configured as a MIPI Master or MIPI Slave supporting camera interface CSI-2 and DSI. The High-Speed signals have a low voltage swing, while Low-Power signals have large swing. High-Speed functions are used for High-Speed data traffic while low power functions are mostly used for control.

The Innosilicon MIPI C-PHY/D-PHY combo is also compatible with MIPI C-PHY v1.1 specification and improves throughput over a bandwidth limited channel, allowing more data without increased signaling clock. It is intended to be used for CSI-2 and DSI. The signaling interface uses a 3-phase transceiver that encodes 3 bit symbols over 3 wires. This is different from the two-wire differential “lane” used in D-PHY. Innosilicon CPHY provides a 3 trio C-PHY v1.1. Symbol encoding to effectively transfer 2.286 bits per symbol. The C-PHY v1.1 operates at up to 3.0GS/s.

MIPI C-PHY:

MIPI D-PHY: